# A Single Threaded Software Architecture for Embedded Systems

### G. Andrew Mangogna

$\begin{array}{c} {\rm May}\ 9,\ 2017\\ {\rm Version}\ 1.8 \end{array}$

© Copyright 2009 - 2017, by G. Andrew Mangogna. Permission to copy and distribute this article by any means is hereby granted by the copyright holder provided the work is distributed in its entirety and this notice appears on all copies.

#### Abstract

This paper is a literate program for a set of software architecture mechanisms that constitute the run time support for a single threaded software architecture domain which is suitable for a large class of applications found in embedded computer systems. The document discusses and explains all the code found in the mechanisms and, as a literate program, can be transformed into the source code for the mechanisms.

# Contents

| 1        | Intr | duction                              | 4  |

|----------|------|--------------------------------------|----|

|          | 1.1  | Scope                                |    |

| <b>2</b> | Ma   | ь Гоор                               | 5  |

| 3        | Ma   | aging Data                           | 10 |

|          | 3.1  | Class Instances                      | 10 |

|          | 3.2  | Instance Allocation                  | 12 |

|          |      | 3.2.1 mechInstCreate                 | 15 |

|          |      | 3.2.2 mechInstDestroy                | 18 |

| 4        | Ma   | aging Execution                      | 20 |

|          | 4.1  | State Machine Rules                  | 20 |

|          | 4.2  | Event Generation                     | 21 |

|          |      | 4.2.1 Event Parameter Storage        | 22 |

|          |      | 4.2.2 Event Control Block            | 23 |

|          |      | 4.2.3 Event Queuing                  | 26 |

|          |      | 4.2.4 Interface for Event Generation | 31 |

|          | 4.0          |                                                                                                                                            |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|          | 4.3          | Delayed Events                                                                                                                             |

|          |              | 4.3.1 mechEventPostDelay                                                                                                                   |

|          |              | 4.3.2 mechEventDelayCancel                                                                                                                 |

|          |              | 4.3.3 mechEventDelayRemaining                                                                                                              |

|          |              | 4.3.4 Delayed Event Queue Operations                                                                                                       |

|          |              | 4.3.5 Expired Events in the Delayed Event Queue                                                                                            |

|          |              | 4.3.6 Timing Considerations                                                                                                                |

|          | 4.4          | Event Dispatch $\ldots \ldots 61$ |

|          |              | 4.4.1 Normal Event Dispatch                                                                                                                |

|          |              | 4.4.2 Polymorphic Event Dispatch                                                                                                           |

|          |              | 4.4.3 Creation Event Dispatch                                                                                                              |

|          |              | 4.4.4 Class Data                                                                                                                           |

|          | 4.5          | Event Dispatch Tracing                                                                                                                     |

|          |              | 4.5.1 Trace Information                                                                                                                    |

|          |              | 4.5.2 Access to Trace Information                                                                                                          |

|          |              | 4.5.3 Tracing Strategies                                                                                                                   |

|          |              |                                                                                                                                            |

| <b>5</b> | Erro         | r Handling 87                                                                                                                              |

|          |              |                                                                                                                                            |

| 6        | Asy          | 104 nchronous Execution 94                                                                                                                 |

|          | 6.1          | Simple Interrupt Priority                                                                                                                  |

| _        |              |                                                                                                                                            |

| 7        | Initi        | alization 100                                                                                                                              |

| 8        | Toat         | ing 101                                                                                                                                    |

| 0        | Test         | ing 101                                                                                                                                    |

| 9        | POS          | IX Specific Interfaces 103                                                                                                                 |

| 0        | 9.1          | POSIX Critical Sections                                                                                                                    |

|          | 9.2          | POSIX Timing Interfaces                                                                                                                    |

|          | 9.2<br>9.3   | POSIX Async Execution Interface                                                                                                            |

|          | 9.4          | POSIX I/O Interface                                                                                                                        |

|          | $9.4 \\ 9.5$ | POSIX Suspending Execution                                                                                                                 |

|          | 9.5<br>9.6   |                                                                                                                                            |

|          | 9.0<br>9.7   | POSIX Initialization    121      POSIX Compilation    122                                                                                  |

|          | 9.1          | POSIX Compilation                                                                                                                          |

| 10       | ARI          | A Cortex-M3 Specific Interfaces 122                                                                                                        |

| 10       |              | Cortex-M3 Critical Sections                                                                                                                |

|          |              | Cortex-M3 Timing Interfaces                                                                                                                |

|          |              | Cortex-M3 Async Execution Interface                                                                                                        |

|          |              | Cortex-M3 Suspending Execution                                                                                                             |

|          |              |                                                                                                                                            |

|          |              | Cortex-M3 Exception Scenarios                                                                                                              |

|          | 10 0         |                                                                                                                                            |

| 11 |                                       | 136 |

|----|---------------------------------------|-----|

|    | 11.1 MSP430 Critical Sections         | 136 |

|    | 11.2 MSP430 Timing Interfaces         | 137 |

|    | 11.3 MSP430 Async Execution Interface | 145 |

|    | 11.4 MSP430 Suspending Execution      | 145 |

|    | 11.5 MSP430 Initialization            | 146 |

| 12 | Source could organization             | 148 |

|    | 12.1 POSIX Version                    | 149 |

|    | 12.2 Cortex-M3 Version                | 152 |

|    | 12.3 MSP430 Version                   | 155 |

| 13 | Copyright                             | 158 |

| 14 | Index                                 | 160 |

# List of Figures

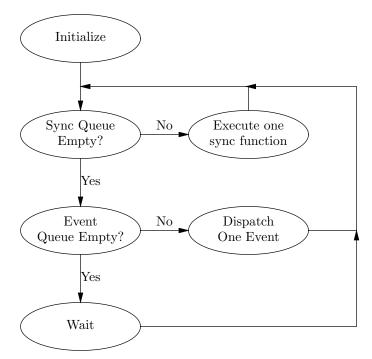

| 1 | Main Loop Flow Diagram                 | 6  |

|---|----------------------------------------|----|

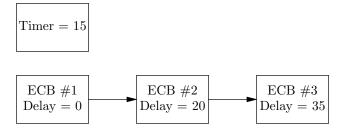

| 2 | Delayed Event Ordering                 | 39 |

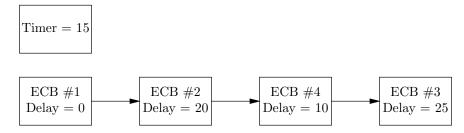

| 3 | Delayed Event Ordering After Insertion | 40 |

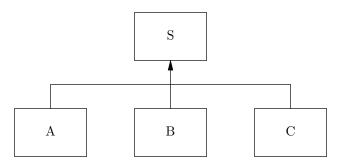

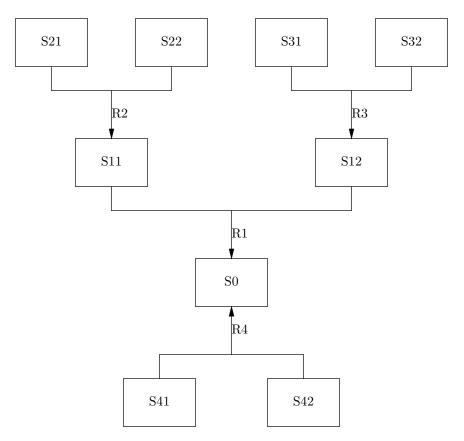

| 4 | Class Generalization Hierarchy         | 69 |

| 5 | Complex Class Generalization Hierarchy | 71 |

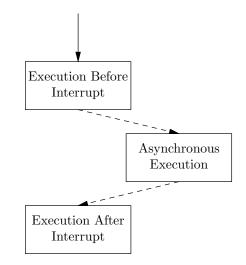

| 6 | Simple Asynchronous Execution          | 95 |

## 1 Introduction

The *Software Architecture Domain* has always been special in Executable UML. It is the domain that specifies the policies for managing data and execution for the system and is the target of model translation. Much of the work of model translation is to generate code in the target implementation language that weaves together the logic of the model actions with invocations of domain operations of the Software Architecture Domain to accomplish the model semantics.

This paper is a literate program for a simple Single Threaded Software Architecture. It implements what can be considered a virtual machine that obeys the execution rules for Executable UML. The implementation language is "C". The mission of a software architecture domain is to implement a set of policy decisions about how data is managed and how execution is sequenced for any system built upon this architecture. The policy decisions made here are oriented toward highly embedded systems that are typically deployed on very minimal computing platforms. As we shall see, the architecture can also be run on POSIX platforms with the primary goal being simulation of the embedded platform.

Policy decisions intended for an embedded micro-controller based platform are unlikely to be optimal for more conventional computing platforms. So we make no claims of universality for this architecture. Indeed it is easy to envision applications which would not be suitable to deploy on a single threaded architecture where there are no separately scheduled execution contexts. It should come as no surprise then that there is not a single Software Architecture Domain suitable for all classes of applications. That is not the point here. What we are trying to accomplish here is to show the implementation of a set of mechanisms for a Software Architecture Domain that does not depend upon the specifics of an application's functionality and is appropriate for any application whose computational demands reasonably match the design criteria of mechanisms.

To divorce the management of data and execution from the application functionality is a more radical concept than might be first recognized. In this paper will we discuss many aspects of execution without any specific reference to what a particular application is attempting to accomplish from a functional point of view. This tends to make the discussion rather abstract and can make it harder to envision how this code might be put to use in any given software application. But remember, this code represents a run-time engine that is the final target of translating an XUML model into a running system. We are discussing a well encapsulated world of data and execution management that is, however unfortunate, completely devoid of any application semantics. This notion often makes many programmers uncomfortable in their belief that everything about a software system is to be tailored to the specific semantics of the application functionality.

The design of STSA is guided by the following criteria:

• There is a very limited budget for running the computing hardware. Of-

ten this limited budget arises from limitation of supplying power to the computing hardware or the need to minimize the costs of the hardware. Consequently, the software execution framework must closely match the facilities directly provided by the hardware. Otherwise, providing capabilities that are not well supported by the hardware platform implies additional software execution that cannot be supported by the computation budget.

• Memory is very limited and typically segmented between that which is read only and that which is read/write with the later type of memory being particularly in short supply.

Certainly, modern computing environments do not tend to suffer from either of these limitations. So we are purposefully targeting limited computing environments as are found in highly embedded control systems and battery powered systems. Often these systems are of a safety critical nature where having very precise control over the software is essential.

#### 1.1 Scope

This literate program discusses many concepts related the Executable UML. There is not space here to give you all the background of this methodology. The reader is referred to some of the many books available on Executable UML for the necessary background [1] [2] [5] [3] [4].

# 2 Main Loop

Let's jump right to the part that you are probably most interested in, the main *loop.* Figure 1 (p. 6) shows a flow diagram of the main loop. The program is an infinite loop. The mechanisms supply the required "C" program function, main. As discussed in the introduction, all the decisions about sequencing program execution are factored away from the application code and incorporated into the mechanisms. After initialization, we enter the loop. The first step is to synchronize to any asynchronous processing that has gone on. Asynchronous processing is discussed in detail in section 6 below (p. 94), but for now we can think of it as interrupts going off and needing to tell the rest of the program that something has happened. The way asynchronous execution does this is to post a function to the sync queue. This constitutes a request that the function be invoked at the first *safe* opportunity during the background processing. From the flow diagram, we see that all sync functions are removed from the sync queue before we consider dispatching any events to a state machine. Although there are no restrictions on what a sync function may do, typically it executes some domain operation that results in generating events to some class instance. Those generated events are placed on the event queue.

After the sync queue is empty, the loop then removes one event from the event queue and dispatches it. In general, dispatching an event will cause a

#### 2 MAIN LOOP

state machine to transition and some state action will execute. State actions may cause other events to be generated. It is required that state actions leave the domain data in a consistent state. We can now see, that outside of a state action is a *safe* time to execute the synchronization functions.

Eventually, the thread of control initiated by some sync function will die out of its own accord. Some state actions perform computations without generating new events and eventually all the events are consumed. At that time, the sync queue will be empty and the event queue will be empty. There is nothing more to do and we then wait. Exactly what it means to *wait* is platform dependent as we shall see.

Figure 1: Main Loop Flow Diagram

We now examine how the general ideas of the main program flow actually get implemented in code. By default, he mechanisms define the program entry point given by the "C" function main. For testing it is convenient to allow the main definition to be elsewhere and we achieve that via conditional compilation.

6

$\langle external \ test \ functions \ 6 \rangle \equiv$

extern void stsa\_main(void) ;

(149 152 155) 100b⊳

```

2 MAIN LOOP

```

```

\overline{7}

\langle main \ loop \ 7 \rangle \equiv

(150 \ 153 \ 156)

#ifdef MECH_TEST

void

stsa_main(void)

#else

int

main(void)

#endif /* MECH_TEST */

{

mechInit() ;

for (;;) { /* Infinite Big Loop */

/*

* Empty the foreground/background sync queue.

*/

\langle background \ sync \ 8 \rangle

/*

* Dispatch one event from the event queue.

*/

if (!mechDispatchOneEvent()) {

/*

\ast Check if this thread of control is complete

* and wait if there is no additional work to

* be done.

*/

mechWait() ;

}

}

}

```

7

#### 2 MAIN LOOP

Not surprising, the main function is an infinite loop. After initialization, the infinite loop is entered. First, we must perform any synchronization between asynchronous foreground execution and the single background thread. This is described in detail in section 6 (p. 94). In most circumstances that means executing the synchronization functions that the foreground processing has requested. The synchronization functions are run as part of the background processing. Also note that the sync queue is emptied before considering any events. This design gives foreground / background synchronization a higher effective priority than the thread of control that might be generated by executing a sync function. For most systems that synchronization is given a simple loop.

```

8 \langle background \ sync \ 8 \rangle \equiv

```

```

(7)

```

#ifndef \_\_ARM\_ARCH\_7M\_\_

/\*

\* Empty the foreground / background

\* synchronization queue.

\*/

while (mechInvokeOneSyncFunc()) {

; /\* empty \*/

}

#endif /\* \_\_ARM\_ARCH\_7M\_\_ \*/

#### 2 MAIN LOOP

As we shall see below (section 10.3, p. 128), for the Cortex-M3 this synchronization is not executed in the main loop but rather in an exception handler. More on this particular processor architecure later, but it does not change the essential characteristic that synchronization occurs first before events are dispatched.

After synchronization is complete, one event is dispatched. The actions executed upon the state transition caused when the event is delivered may very well generate other events into the event queue. However, after each dispatched event, we determine if there is any synchronization that must occur. In this way, events are removed and dispatched from the event queue one at a time checking if there are any sync functions that must be executing in between. Note that in this design, the event queue is not placed in a critical section. Interrupts are *not* allowed direct access to the event queue. Asynchronous execution has only one method to request computation and that is the sync queue.

Eventually, we will run out of work to  $do^1$ . It is then time to wait for the next thing to come along. What it means to wait is also platform dependent. For bare metal systems, particularly low power ones, the processor will be put to sleep to save power. On an operating system, there are system specific means to cause the process to sleep. The implementation must be careful in determining that we indeed are ready to wait. We must be able to test for an empty sync queue and wait as a single atomic action. We will see how that happens in section 9.5 (p. 118) below.

An important thing to remember here is that this represents all the flow of execution policy for the entire system. No part of the application code determines when a state machine event is dispatched. Too many times, code which decides what to do next is scattered throughout a program. This code is often inconsistent, many times just wrong and carries a large testing and maintainence burden. It is unnecessary to do that. Careful factoring of execution sequencing away from the application code can place all the policy decisions in a very small amount of code. Your system may need different a policy to meet the computational demands of your applications, but that does not mean that the execution policy must be tailored for every distinct application. Software architectures can meet the computation requirements of large classes of applications and do so in a manner that is independent of the subject matter of the application.

The careful reader will have already recognized that there is no way to exit the program directly. This is in keeping with the highly embedded nature of the class of applications for which STSA is intended. Your system may need a way to terminate and if it does, then you should insert the termination check just before the call to mechWait. This allows the ongoing thread of control to complete before termination.

<sup>&</sup>lt;sup>1</sup>or else we have some type of unbounded computation

#### 3 Managing Data

The STSA was designed for highly embedded systems. These types of systems often tend to be long running, *i.e.* the program is intended to run for the lifetime of the system without ever stopping. This means that there is no opportunity to restart and clean up if something goes wrong. Safety critical systems, for example, just do not have that luxury. The long running nature of embedded applications has led to the general notion among embedded programmers that a central system heap is a bad idea. A heap can fragment and at critical times not have sufficient contiguous memory to allocate an essential data structure. Whether or not use of a heap is a bad idea in these types of systems is subject to some skepticism. I don't know of any definitive studies, but the conventional wisdom is well entrenched.

What is used instead is fixed, worst case allocation. It is less efficient in the way that memory is utilized, but tends to be more deterministic in the way that it behaves. A heap can introduce probabilistic behavior. At least with fixed allocation and a good set of test cases, you can have reasonable assurances that memory resources are properly allocated and released.

As you will see below, all data is allocated in fixed sized pools, the size of which are determined at compile time. This includes internal data structures as well as those holding the application instance data. This may take some of the non-deterministic behavior out of the allocation, but it does not make the job of estimating the proper sizes of the memory pools any easier. This is usually accomplished by simple characterization, *i.e.* testing it to failure and determining the best size for things...

#### 3.1Class Instances

In order to keep track of the essential status of instances, all instance structures include a data structure as its first member. This is the view that the mechanisms take of an instance and the mechanisms cast all instance pointers to this data type. In object oriented parlance, you can think of this as the base class for all instances.

10

(149 152 155) 12⊳

```

\langle data \ types \ 10 \rangle \equiv

typedef struct mechinstance {

AllocCount alloc ;

StateCode currentState ;

struct mechclass const *instClass ;

} *MechInstance ;

Defines:

MechInstance, used in chunks 12, 14-16, 18b, 19, 24, 31-34, 37, 38, 44-49, 65, 75, 78,

and 84-86.

```

The alloc member is used to determine if a particular storage slot is currently in use. If alloc is 0, then the slot is free. A non-zero value indicates that an instance is allocated to that slot. This member also plays an important role in detecting the *event-in-flight* error as we shall see below (see section 4.4.1, p. 68). A small 8-bit quantity is sufficient for this member.

⟨base types 11a⟩≡ (149 152 155) 11b▷

typedef uint8\_t AllocCount ;

Defines:

uint8\_t, used in chunk 139.

The currentState member holds the value of the current state for the instance.

11b (base types 11a)+≡

typedef uint8\_t StateCode ;

11a

(149 152 155) ⊲11a 21⊳

Defines:

uint8\_t, used in chunk 139.

As we see from the data type, states are held in 8 bit quantities and this limits the number of states that a class may have to 253. Why 253? Two of the values in the state type are used to indicate if a given event is to be ignored or treated as a fatal error.

11c

(149 152 155) 22 ⊳

Defines:

$\langle constants | 11c \rangle \equiv$

MECH\_STATECODE\_CH, used in chunk 65. MECH\_STATECODE\_IG, used in chunk 65.

#define MECH\_STATECODE\_IG UINT8\_MAX

#define MECH\_STATECODE\_CH (UINT8\_MAX - 1)

We use the two highest values of a StateCode to indicate ignored and can't happen, respectively. The semantics of ignoring an event and deeming an event as not possible to happen are explained below. In practice, 253 states would be an enormous state model and clear indication that you should rethink your design.

The instClass member is a pointer to a data structure that defines the class. The class data structure is discussed below (section 4.4.4, p. 79). For now, we can think of it as the data structure that holds all the information that is invariant for the class, *i.e.* the information that applies to all instances of the class.

#### 3.2 Instance Allocation

There are three ways to create an instance:

- 1. Create an instance as part of an initial instance population.

- 2. Create an instance synchronously to the execution of some action by invoking a function.

- 3. Create an instance asynchronously to the execution of some action by sending an event.

The initial instance population consists of defining the storage pool for the class to have initial values. In "C" this is nothing more than defining an array with initializers, since we use simple "C" arrays as the storage pools. This can be a tedious undertaking, but the mechanisms provide no support for these definitions since this is really a compile time undertaking. Tools such as pycca<sup>2</sup> can significantly ease the tedium. In this section we are going to discuss synchronous instance creation. This is instance creation by a direct function invocation. Later we will discuss asynchronous instance creation which is instance creation by generating an event.

Instance allocation also supports a very simplified notion of construction and destruction for the instances. This is no where near as complicated or full featured as something in C++. Constructors and destructors take no arguments other than a pointer to the instance.

(149 152 155) ⊲10 13⊳

```

⟨data types 10⟩+≡

typedef void (*InstCtor)(MechInstance);

typedef void (*InstDtor)(MechInstance);

Defines:

InstCtor, used in chunk 13.

InstDtor, used in chunk 13.

Uses MechInstance 10.

```

12

<sup>&</sup>lt;sup>2</sup>See http://tcl-cm3.sourceforge.net/

$\langle data \ types \ 10 \rangle + \equiv$

It is primarily useful for when the instance has a more complicated data structure as an attribute. If you need to do complicated construction of instances, the preferred method is to do that with an instance based operation or as part of a state action for an asynchronously created instance.

To support managing a pool of class instances, an **Instance Allocation Block**, or **IAB** for short, data structure is used to keep track of the memory pool.

13

```

(149 152 155) ⊲12 23a⊳

```

typedef struct installocblock {

void \*storageStart ;

void \*storageFinish ;

void \*storageLast ;

AllocCount allocCounter ;

size\_t instanceSize ;

InstCtor construct ;

InstDtor destruct ;

} \*InstAllocBlock ;

Defines:

InstAllocBlock, used in chunks 14, 16–19, and 79b. Uses InstCtor 12 and InstDtor 12.

What we need is a data structure that can find the bounds of the pool.

- storageStart A pointer to the beginning of the memory where the instance storage pool is located. Typically this is an array allocated to hold the instances of a class.

- storageFinish A pointer to one element beyond the end of the instance storage pool for the class. This pointer may not be dereferenced, of course, but provides the boundary marker for the end of the pool.

- storageLast A pointer to the instance that was last allocated. This is used as the starting point for allocating the next instance.

- instanceSize The number of bytes of memory occupied by an instance.

- construct A pointer to a constructor function. If there is no constructor defined for the class, then the value of this member may be set to NULL.

- destruct A pointer to a destructor function. If there is no destructor defined for the class, then the value of this member may be set to NULL.

As we shall see, the underlying allocation algorithm is a simple linear search.

```

(instance functions 14) \equiv

(150 153 156) 16⊳

14

static MechInstance

mechInstFindSlot(

MechClass instClass)

ſ

assert(instClass != NULL) ;

InstAllocBlock iab = instClass->iab ;

if (iab == NULL) {

return NULL ;

}

assert(iab->storageLast < iab->storageFinish) ;

/*

* Search for an empty slot in the pool.

*/

MechInstance inst ;

for (inst = mechInstNext(iab, iab->storageLast) ;

inst->alloc != 0 && inst != iab->storageLast ;

inst = mechInstNext(iab, inst)) {

/*

* Empty

*/

}

/*

* Check if we ended up on a slot that is not allocated.

*/

return inst->alloc == 0 ? inst : NULL ;

```

## }

Uses InstAllocBlock 13 and MechInstance 10.

## 3.2.1 mechInstCreate

$\langle external \ scoped \ functions \ 15 \rangle \equiv$

The function, mechInstCreate, is used to synchronously create an instance of a class.

15

(149 152 155) 18b⊳

```

extern MechInstance mechInstCreate(

MechClass instClass,

StateCode initialState);

Uses MechInstance 10.

```

It takes as arguments:

instClass A pointer to the class structure for the instance to be created.

initialState The state number into which the instance will be placed. For classes that do not have an associated state model this argument should be set to 0.

The return value of the function is a pointer to the new created instance. Since the return type of the function is MechInstance, in general it will have to be cast to be a pointer to the correct class structure type.

```

16

```

```

\langle instance \ functions \ 14 \rangle + \equiv

(150 153 156) ⊲14 19⊳

MechInstance

mechInstCreate(

MechClass instClass,

StateCode initialState)

{

assert(instClass != NULL) ;

InstAllocBlock iab = instClass->iab ;

#ifndef NDEBUG

if (instClass->odb) {

assert(initialState < instClass->odb->stateCount) ;

}

#endif /* NDEBUG */

/*

* Search for an empty slot in the pool.

*/

MechInstance inst = mechInstFindSlot(instClass) ;

if (inst == NULL) {

mechFatalError(mechNoInstSlot, instClass) ;

}

/*

* Record where we left off for the next time around.

*/

iab->storageLast = inst ;

/*

* Mark the slot as in use.

*/

inst->alloc = mechInstIncrCounter(iab) ;

inst->currentState = initialState ;

inst->instClass = instClass ;

/*

* Run the constructor if there is one.

*/

if (iab->construct) {

iab->construct(inst) ;

```

} return inst ;

}

Uses InstAllocBlock 13 and MechInstance 10.

As we can see it is a simple linear search of the pool looking for an empty slot to allocate. The **storageLast** member of the IAB is used as a starting location for the search. This attempts to improve the search speed on the assumption that the next free slot is most likely to be in the location after the last allocated one. It is a fatal system error to run out of instance storage space.

Since the pool is allocated in a contiguous block of memory, we must wrap around the iterator when it passes the end of the storage pool. That is accomplished with the mechInstNext function.

```

17

```

$\langle instance \ allocation \ helper \ 17 \rangle \equiv$ static inline void \* mechInstNext( InstAllocBlock iab, void \*ptr) { ptr = (char \*)ptr + iab->instanceSize ; if (ptr >= iab->storageFinish) { ptr = iab->storageStart ; } return ptr ; } Defines: inline, used in chunk 101b. Uses InstAllocBlock 13.

(150 153 156) 18a⊳

It is very important to understand that a synchronously allocated instance does *not* run a state action. The instance may be placed into any valid state for the class, but as is seen above, no code is run other than the constructor. This is by design. If you need state action code executed when an instance is created then it is necessary to use asynchronous instance creation by generating a creation event. Alternatively, an event can be generated to the newly created instance immediately after it has been constructed. Both mechanisms have their uses, although the synchronous instance creation is probably overused in many designs since it is what most programmers are familiar with.

One other important point here. There is a counter in the IAB that is incremented each time an instance is allocated and this value is used in the alloc member of the instance. This is another part of the strategy to detect an *event-in-flight* error. This is described further below (p. 68). The effect of running this counter is that every instance gets a different alloc member value (modulo 255, naturally). The increment has one little catch. You cannot increment the counter and leave it at zero.

```

(instance allocation helper 17) + \equiv

18a

(150\ 153\ 156) \triangleleft 17

static inline

AllocCount

mechInstIncrCounter(

InstAllocBlock iab)

{

/*

* Catch any wrap around to zero.

*/

if (++iab->allocCounter == 0) {

++iab->allocCounter ;

}

return iab->allocCounter ;

}

Defines:

inline, used in chunk 101b.

Uses InstAllocBlock 13.

```

#### 3.2.2 mechInstDestroy

18b

The function, mechInstDestroy, is used to synchronously destroy an instance.

(149 152 155) ⊲15 31b⊳

```

{external scoped functions 15⟩+≡

extern void mechInstDestroy(

MechInstance inst) ;

Uses MechInstance 10.

```

It takes a single argument:

inst A pointer to an instance to be destroyed.

Just as there was a distinction between synchronous and asynchronous instance creation, there is a similar distinction for destruction. Asynchronous destruction happens as a result of an instance entering an **final** state and that is discussed further below. Here we are dealing with synchronous destruction of an instance.

```

19

```

```

\langle instance \ functions \ 14 \rangle + \equiv

(150 153 156) ⊲16 94⊳

void

mechInstDestroy(

MechInstance inst)

{

InstAllocBlock iab = inst->instClass->iab ;

assert(iab != NULL) ;

/*

* Run the destructor, if there is one.

*/

if (iab->destruct) {

iab->destruct(inst) ;

}

/*

* Mark the slot as free.

*/

inst->alloc = 0 ;

}

```

Uses InstAllocBlock 13 and MechInstance 10.

Destroying an instance is a very simple matter indeed. If there is a destructor, it is run. The slot is free when its **alloc** member has a value of 0. But beware, for designs that have complicated relationships among the classes, instance deletion can be very complicated, requiring much care that the interdependencies among classes are properly preserved. That work is not done here! You will have to include it in your action code.

# 4 Managing Execution

In this section we discuss the rules and policies associated with managing the sequencing of execution. There are two means available to an application to control the sequencing of execution.

- 1. Invoke an ordinary function.

- 2. Generate an event to the instance of a class.

Not much needs to be said about invoking functions. Computation transfers to the entry point and runs until the function is complete, transferring control back to next statement of the caller. Typically, such functions are organized into those that are associated with the domain as whole, a particular class or instances of a class. Such organization may be helpful to the programmer, but since they are directly supported by the implementation language, STSA does not get involved in mediating them.

Where STSA does get involved is for those computation that must leave off at some point, waiting for some other action in the system or the external environment, and then resume execution maintaining the past history. This type of execution is implemented as a state machine.

### 4.1 State Machine Rules

Each class that has lifecycle behavior may have a state model associated with it and each instance of that class will have a state variable. STSA supports a Moore type state model.

In the Moore formulation of state models, action code is associated with states and is executed upon entry into a state. This is distinguished from the Mealy formulation where actions are associated with the transitions and are executed upon exiting a state. Much writing and discussion has been wasted attempting to justify one type of state model over another. What we know is that they are computationally equivalent, *i.e.* we can prove that there is no problem that you can solve with a Moore machine that cannot also be solved with a Mealy machine and *vice versa*. Whether your application is easier to describe with one type rather than the other is something that you alone may decide. Moore machines are the traditional formulation for Executable UML and they have the simplest implementation structures. What we specifically reject here is any use of hierarchical state models. They are unnecessary and

add complication that is not welcome. The power of computation in Executable UML is derived from the interaction of simple state machines each of which is tied to the lifecycle of a particular class. If you have some state model that is large and complicated where you think some other kind of higher order structure is needed, the usual reason is that you have multiple classes masquerading as one and further refinement of your analysis is necessary.

Generally, state actions affect other computations in the domain by updating instance attribute values or by generating events to other instances. The important distinction here is that the application code of the state actions does not deal with actually dispatching the events nor does it control which event is dispatched next.

### 4.2 Event Generation

There are three types of events:

- 1. Ordinary events that cause transitions in state machines.

- 2. Polymorphic events that are mapped at runtime across a generalization hierarchy.

- 3. Creations events that support asynchronous instance creation.

We will have need to distinguish the various event types and define and enumeration to do that.

21

(149 152 155) ⊲11b 23b⊳

```

{base types 11a}+=

typedef enum {

NormalEvent,

PolymorphicEvent,

CreationEvent

} MechEventType ;

Defines:

```

MechEventType, used in chunks 24, 31a, 74a, 81, and 85.

The process of generating an event involves the following steps:

#### 1. Obtain an **Event Control Block** from the free pool of ECB's.

- 2. Set the values of the fields in the ECB.

- 3. Queue the ECB for later dispatch.

#### 4.2.1**Event Parameter Storage**

Before we can talk about what an ECB contains, we need to deal first with events that carry parametric data. In this formulation of state machines, events may carry additional parameters. Clearly space has to be allocated for that data. The more difficult issue is to deal with the type of the parameter data. There are a couple of solutions, neither of which is very satisfying. We could collect all the parameters from all the state machines in the system and create a giant union. This would properly allocate the amount of parameter storage required and provide a type safe manner to deal with that data. Unfortunately, the parameters to states are scattered in very many places in a system and gathering them together is a difficult undertaking.

Here we take the view of providing some generic parameter fields with a fixed amount of memory and letting state actions cast that memory into the appropriate type. Needless to say, this can also be a source of errors, but is much easier to manage. Choose the technique that makes the most sense for your system. In many systems, the number of states that use parametric data is small and using a fixed size works better than might be expected. The important point here is that events can carry data with them. Many state machine formulations don't support this and it is very difficult to correctly manage memory lifetime without it. It is one of those things that you might not use very often but it is difficult to do without when you need it.

We fix the amount of memory used for event parameter storage, allowing it to be overridden by the compiler command.

22

#

$\langle constants \ 11c \rangle + \equiv$

(149 152 155) ⊲11c 28a⊳

#ifndef MECH\_ECB\_PARAM\_SIZE define MECH\_ECB\_PARAM\_SIZE 16

#endif /\* MECH\_ECB\_PARAM\_SIZE \*/

Here we define a union of arrays for some common types. It is not exhaustive (N.B. no floats or doubles).

(data types 10)+= (149 152 155) <13 63>

typedef union {

signed char cparm[MECH\_ECB\_PARAM\_SIZE] ;

unsigned char ucparm[MECH\_ECB\_PARAM\_SIZE] ;

unsigned short usparm[MECH\_ECB\_PARAM\_SIZE / sizeof(unsigned short)] ;

signed short isparm[MECH\_ECB\_PARAM\_SIZE / sizeof(signed short)] ;

unsigned uparm[MECH\_ECB\_PARAM\_SIZE / sizeof(unsigned)] ;

int iparm[MECH\_ECB\_PARAM\_SIZE / sizeof(unsigned)] ;

unsigned long ulparm[MECH\_ECB\_PARAM\_SIZE / sizeof(unsigned long)] ;

signed long ilparm[MECH\_ECB\_PARAM\_SIZE / sizeof(signed long)] ;

void \*pparm[MECH\_ECB\_PARAM\_SIZE / sizeof(void \*)] ;

} EventParamType ;

Defines:

23a

EventParamType, used in chunks 24 and 96c.

State actions may use the fields in the above union, or cast the whole thing to a type they like better. It is necessary that the code that generates the event and the code that consumes the event have the same idea of how the data will be treated.

#### 4.2.2 Event Control Block

With that diversion done, on to the Event Control Block itself. The ECB is the primary data structure for generating and dispatching events.

First some data types. Events are reference counted and 8 bits are deemed sufficient for that. More on reference counting ECB's below (p. 25).

⟨base types 11a⟩+≡ (149 152 155) ⊲21 23c ▷

typedef uint8\_t RefCount ;

Defines:

uint8\_t, used in chunk 139.

Events are also encoded as small zero based sequential integers.

23c  $\langle base \ types \ 11a \rangle + \equiv$

23b

(149 152 155) ⊲23b 40⊳

Defines:

typedef uint8\_t EventCode ;

uint8\_t, used in chunk 139.

Event queuing is done by doubly linked lists and the links are allocated as part of the ECB as the **next** and **prev** members. We also allocate a separate ECB structure to use as the event queue terminus.

```

\langle event \ data \ types \ 24 \rangle \equiv

24

(149 \ 152 \ 155)

typedef struct mechecb {

struct mechecb *next ;

struct mechecb *prev ;

RefCount referenceCount ;

EventCode eventNumber ;

AllocCount alloc ;

MechEventType eventType ;

union {

MechInstance targetInst ;

MechClass targetClass ;

} instOrClass ;

MechInstance srcInst ;

MechDelayTime delay ;

EventParamType eventParameters ;

} *MechEcb ;

Defines:

MechEcb, used in chunks 26, 27, 29-36, 41, 42, 46, 48-50, 52-56, 59, 61, 62, 65, 75, 78,

102c, and 130b.

Uses EventParamType 23a, MechDelayTime 40, MechEventType 21, and MechInstance 10.

```

An ECB is reference counted and that count is stored in the referenceCount member. Normally, all the reference counting is handled internally by the event generation and dispatch code. However, it is sometimes the case that a given event will need to be generated repeatedly. Rather than go through all the steps of event generation, you can use the reference count to prevent an ECB from being returned to the pool. By allocating the ECB, either from the pool using mechEventAlloc or as an ordinary variable, and then incrementing the reference count, the mechanisms will not return the ECB to the free pool after the event is dispatched. This also allows the ECB to be allocated in memory that is not in the normal ECB pool that is maintained by the mechanisms. Note that this is an optimization that carries with it the potential for bleeding ECB data structures and loosing them forever along with a number of other abuses of variable lifetime. It should be used with care and certainly if you need to generate high rate periodic events you should consider different design options (such as dedicated hardware timers).

The eventNumber member holds the value of the event encoded as a small non-negative number. Event numbers are ultimately used as an array index and therefore must be encoded as zero based sequential integers. The encoding is very tedious to keep maintained and again some tooling like the **pycca** program is helpful in this regard.

The alloc member is yet another part of *event-in-flight* detection (see page 68). We will discuss that more below when we discuss event dispatch. For now, this member of the ECB holds the value of the allocation counter for the instance that is the target of the event. So when an event is generated, a copy of the current value of the alloc member of the instance is stored in the ECB. I'm sure you can see where this is going.

The eventType member describes which of the three types of events this ECB is being used for. It also helps discriminate the anonymous union of targetInst and targetClass. For normal and polymorphic events, the events are directed at a class instance and therefore the targetInst member is used. For creation events, the events are directed, conceptually, at a class and the targetClass member is used.

The srcInst member records the instance pointer of the instance that generates the event. If the event is generated outside the context of an instance (*e.g.* in an domain operation), then this member value is set to NULL. The srcInst member also serves an important role in enforcing the rules for delayed events. More on that later.

The **delay** member is used in delayed event generation. We discuss delayed events in detail in section 4.3 (p. 39).

Finally, the eventParameters member holds parametric data for this event.

Note that there is no notion of priority contained in the ECB. Some software architectures queue events in a priority order. That is not supported here. Frankly, if you need event priorities to make your system work, then you need to revisit your design or look for a software architecture that supports multiple threads of execution.

#### 4.2.3 Event Queuing

The last step in event generation is to queue the event. In this architecture, we do asynchronous event dispatch. This insures that the state actions are atomic. Since a queue is used, as a state action executes and generates an event, we know that event will not be dispatched until after the state action completes. Therefore, there is no danger of a long complicated chain of event dispatching cycling back around to alter the state of the instance or potentially modify some data that the state action accesses after generating the event. The guaranteed of atomic state action execution is very important. We now examine the code that performs the queueing.

This code is very conventional and I'm sure you seen it or something very much like it many times before. There are only a of operations on the queue. We need to determine the beginning and end of the queue as event are queue in order of generation.

```

26a

```

```

\langle event \ queues \ 26a \rangle \equiv

static inline

struct mechecb *

eventQueueBegin(

MechEcb iter)

{

return iter->next ;

}

Defines.

inline, used in chunk 101b.

Uses MechEcb 24.

\langle event \ queues \ 26a \rangle + \equiv

static inline

struct mechecb *

eventQueueEnd(

MechEcb iter)

{

return iter ;

}

Defines:

inline, used in chunk 101b.

Uses MechEcb 24.

```

(150 153 156) ⊲26a 27a⊳

(150 153 156) 26b⊳

26b

We need to be able to determine if a queue is empty.

27a

(150 153 156) ⊲26b 27b⊳

```

{event queues 26a}+=

static inline

bool

eventQueueEmpty(

MechEcb iter)

{

return iter->next == iter ;

}

Defines:

inline, used in chunk 101b.

Uses MechEcb 24.

```

And finally, we need to be able to insert and remove entries. Insertion places the ECB pointed to by item in the queue immediately before the ECB pointed to by at.

```

27b

```

27c

```

\langle event \ queues \ 26a \rangle + \equiv

(150 153 156) ⊲27a 27c⊳

static inline

void

eventQueueInsert(

MechEcb item,

MechEcb at)

{

item->prev = at->prev ;

item->next = at ;

at->prev->next = item ;

at->prev = item ;

}

Defines:

inline, used in chunk 101b.

Uses MechEcb 24.

Removal simply links around the ECB pointed to by item.

\langle event \ queues \ 26a \rangle + \equiv

(150 153 156) ⊲27b 28b⊳

static inline

void

eventQueueRemove(

MechEcb item)

{

item->prev->next = item->next ;

item->next->prev = item->prev ;

}

Defines:

inline, used in chunk 101b.

Uses MechEcb 24.

```

Like all the other data structures, there is a storage pool for ECB's and we define a size for it here that can be overridden on the compiler command line. Sizing the pool for ECB's can be difficult. It must be worst case allocation as running out of ECB's is a fatal system error. The pool must be sized to account for the maximum number of events that can be in flight at the same time. This includes delayed events, since they can be considered to be slow flying events.

28a

#### (149 152 155) ⊲22 79a⊳

#ifndef MECH\_EVENTPOOLSIZE

# define MECH\_EVENTPOOLSIZE 10

#endif /\* MECH\_EVENTPOOLSIZE \*/

We must allocate the memory for the ECB storage. As usual, storage is just an array of structures.

28b (event queues 26a)+≡ (150 153 156) ⊲27c 28c⊳ static struct mechecb mechECBPool[MECH\_EVENTPOOLSIZE];

Defines:

mechECBPool, used in chunk 29.

There are four queues that are used to manage events. Note that all the queues are initialized to be empty, *i.e.* their **next** and **prev** members point back to the queue head itself.

28c  $\langle event \ queues \ 26a \rangle + \equiv$

$\langle constants \ 11c \rangle + \equiv$

(150 153 156) ⊲28b 29⊳

static struct mechecb eventQueue ;

static struct mechecb delayedEventQueue ;

static struct mechecb freeEventQueue ;

Defines:

delayedEventQueue, used in chunks 29, 42, 46, 48, 50, and 52-56. eventQueue, used in chunks 29, 35b, 36, 46, 54, 102c, 130b, and 132. freeEventQueue, used in chunks 29, 30, and 93b.

29

The eventQueue queue holds all events waiting to be dispatched. The delayedEventQueue queue holds events that are to be delivered by the mechanisms at some time in the future. Finally, the freeEventQueue queue holds those ECB's that are not currently begin used. From the data structures and the semantics of the queuing, a given ECB can be on at most one of the queues at any time. Most of the time each ECB is on exactly one of the queues, but there are short times when ECB's are held in local variables or they can even be held in domain variables.

Since we have a pool of ECB's, we need some operations to manage the pool. We start with initialization. This places all the ECB's in the pool onto the free event queue.

```

\langle event \ queues \ 26a \rangle + \equiv

(150 153 156) ⊲28c 30a⊳

static void

mechEventInit(void)

{

assert(MECH_EVENTPOOLSIZE >= 1) ;

/*

* Initialize the ECB used as the queue terminus.

*/

eventQueue.next = eventQueue.prev = &eventQueue ;

delayedEventQueue.next = delayedEventQueue.prev =

&delayedEventQueue ;

freeEventQueue.next = freeEventQueue.prev = &freeEventQueue ;

/*

* Place all the event control blocks on the free event

* queue. Allocation occurs from there.

*/

for (MechEcb ecb = mechECBPool ;

ecb < mechECBPool + MECH_EVENTPOOLSIZE ; ++ecb) {</pre>

eventQueueInsert(ecb, &freeEventQueue) ;

}

}

Uses delayedEventQueue 28c, eventQueue 28c, freeEventQueue 28c, MechEcb 24,

```

and mechECBPool 28b.

Event allocation is just removing an ECB from the free list. N.B. that running out of Event Control Blocks is fatal.

```

30a

\langle event \ queues \ 26a \rangle + \equiv

(150 153 156) ⊲29 30b⊳

static inline

MechEcb

mechEventAlloc(void)

{

if (eventQueueEmpty(&freeEventQueue)) {

mechFatalError(mechNoECB) ;

}

MechEcb ecb = freeEventQueue.next ;

eventQueueRemove(ecb) ;

ecb->referenceCount = 0 ;

return ecb ;

}

Defines:

inline, used in chunk 101b.

Uses freeEventQueue 28c and MechEcb 24.

Finally, deletion returns ECB's to the free queue.

30b

\langle event \ queues \ 26a \rangle + \equiv

(150 153 156) ⊲30a

static void

mechEventDelete(

MechEcb ecb)

{

assert(ecb != NULL) ;

if (ecb->referenceCount <= 1) {</pre>

eventQueueInsert(ecb, &freeEventQueue) ;

} else {

--ecb->referenceCount ;

}

}

```

Uses freeEventQueue 28c and MechEcb 24.

Note that ECB's are returned to the free queue only when their reference count goes to zero. The test, if (ecb->referenceCount <= 1), is used since the referenceCount member is unsigned and we want to free the ECB if its reference count is either 0 or 1 when it is passed to this function. This allows an invocation of mechEventAlloc followed immediately by an invocation of mechEventDelete to properly free the ECB. Blindly decrementing the referenceCount will cause it to roll over when it is 0.

#### 4.2.4 Interface for Event Generation

Finally, we can get to functions that the mechanisms provide for a state action to generate an event.

One step in generating an event is to fill in the ECB members. Much of that step is common among the three types of events and we can factor that into a constructor type function.

```

31a

```

31b

```

\langle event \ generate \ 31a \rangle \equiv

(150 153 156) 32a⊳

static inline

MechEcb

mechEventCtor(

EventCode event,

MechEventType type,

MechInstance targetInst,

MechInstance srcInst)

{

MechEcb ecb = mechEventAlloc() ;

ecb->eventNumber = event ;

ecb->eventType = type ;

ecb->instOrClass.targetInst = targetInst ;

ecb->srcInst = srcInst ;

return ecb ;

}

Defines.

inline, used in chunk 101b.

Uses MechEcb 24, MechEventType 21, and MechInstance 10.

First we consider the step of obtaining an ECB. For normal events the

mechEventNew function is provided.

\langle external \ scoped \ functions \ 15 \rangle + \equiv

(149 152 155) ⊲18b 32b⊳

extern MechEcb mechEventNew(

EventCode event,

MechInstance targetInst,

MechInstance srcInst);

Uses MechEcb 24 and MechInstance 10.

```

event The number of the event.

targetInst A pointer to the instance structure that is to receive the event.

srcInst A pointer to the instance structure that is sending the event. Events generated outside of a class instance may set this argument to NULL.

This function returns an ECB for a normal event that has all its internal members initialized properly.

```

32a

```

32b

```

\langle event \ generate \ 31a \rangle + \equiv

(150 153 156) ⊲31a 33a⊳

MechEcb

mechEventNew(

EventCode event,

MechInstance targetInst,

MechInstance srcInst)

{

assert(targetInst != NULL) ;

assert(targetInst->alloc != 0) ;

assert(targetInst->instClass != NULL) ;

assert(targetInst->instClass->odb != NULL) ;

MechEcb ecb = mechEventCtor(event, NormalEvent, targetInst,

srcInst) ;

/*

* Take a copy of the alloc member for event-in-flight

* detection.

*/

ecb->alloc = targetInst->alloc ;

return ecb ;

}

```

Uses MechEcb 24 and MechInstance 10.

Note the assignment of the the alloc member from the instance into the alloc member of the ECB. This is yet another part of the *event-in-flight* detection (see page 68).

As you might expect, there is a corresponding function for each of the other two event types.

{external scoped functions 15}+= (149 152 155) ⊲31b 33b> extern MechEcb mechPolyEventNew( EventCode event, MechInstance targetInst, MechInstance srcInst) ; Uses MechEcb 24 and MechInstance 10.

32

- event The number of the event. *N.B.* the event number here is the event number of the polymorphic event as encoded for a class that serves as a supertype in a generalization hierarchy.

- targetInst A pointer to the instance structure that is to receive the event.

- srcInst A pointer to the instance structure that is sending the event. Events generated outside of a class instance may set this argument to NULL.

```

33a

\langle event \ generate \ 31a \rangle + \equiv

(150 153 156) ⊲32a 34a⊳

MechEcb

mechPolyEventNew(

EventCode event,

MechInstance targetInst,

MechInstance srcInst)

{

assert(targetInst != NULL) ;

assert(targetInst->instClass != NULL) ;

assert(targetInst->instClass->pdb != NULL) ;

MechEcb ecb = mechEventCtor(event, PolymorphicEvent,

targetInst, srcInst) ;

return ecb ;

}

```

Uses MechEcb 24 and MechInstance 10.

$\langle external \ scoped \ functions \ 15 \rangle + \equiv$

Note that the **alloc** member is not assigned to for polymorphic events. This is because polymorphic events are never delivered to an instance. They are mapped at run time to a normal event which is delivered to the instance.

33b

(149 152 155) ⊲32b 35a⊳

extern MechEcb mechCreationEventNew( EventCode event, MechClass targetClass, MechInstance srcInst); Uses MechEcb 24 and MechInstance 10.

```

\langle event \ generate \ 31a \rangle + \equiv

34a

(150 153 156) ⊲33a 34b⊳

MechEcb

mechCreationEventNew(

EventCode event,

MechClass targetClass,

MechInstance srcInst)

{

assert(targetClass != NULL) ;

assert(targetClass->iab != NULL) ;

assert(targetClass->odb != NULL) ;

MechEcb ecb = mechEventAlloc() ;

ecb->eventNumber = event ;

ecb->eventType = CreationEvent ;

ecb->instOrClass.targetClass = targetClass ;

ecb->srcInst = srcInst ;

ecb \rightarrow alloc = 0;

return ecb ;

}

Uses MechEcb 24 and MechInstance 10.

```

Creation events are different enough that the mechEventCtor function is not that useful and the initialization is more easily accomplished directly.

As discussed above, ECB's are reference counted. Internally, the mechanisms use the function below to increment the reference count for an ECB before it is inserted into a queue.

```

34b

```

```

{event generate 31a}+=

static inline

RefCount

mechEventIncrRef(

MechEcb ecb)

{

return ++ecb->referenceCount ;

}

Defines:

inline, used in chunk 101b.

Uses MechEcb 24.

```

(150 153 156) ⊲34a 35b⊳

There is no corresponding function to decrement the reference count as mechEventDelete serves that role.

Once you have obtained an ECB initialized for the proper type of the event, then you need to fill in any event parameter data. Frequently, there are none. Then the ECB is ready to be placed on a queue. As mentioned before, there is a distinction between events an instance sends to itself and those that an instance sends to a different instance. Self directed events are placed on the front of the event queue so that they are dispatched in preference to the nonself directed events. It is important to place the ECB in the correct position on the event queue, but the mechanisms provide no guarantees for this other than the assistance of an assertion.

To queue a non-self directed event, the function mechEventPost is invoked.

```

(external scoped functions 15)+≡ (149 152 155) ⊲ 33b 35c⊳

extern void mechEventPost(MechEcb ecb);

```

Uses MechEcb 24.

35a

ecb A pointer to an event control block (ECB). The ECB must be the return value from mechEventNew, mechPolyEventNew or mechCreationEventNew.

The code is very straight forward. The reference count of the ECB is incremented and it is queued to the rear of the event queue.

```

\langle event \ generate \ 31a \rangle + \equiv

35b

(150 153 156) ⊲34b 36⊳

void

mechEventPost(

MechEcb ecb)

{

mechEventIncrRef(ecb) ;

eventQueueInsert(ecb, &eventQueue) ;

}

Uses eventQueue 28c and MechEcb 24.

To queue a self directed event, the function mechEventPostSelf is invoked.

\langle external \ scoped \ functions \ 15 \rangle + \equiv

(149 152 155) ⊲35a 41 ⊳

35c

extern void mechEventPostSelf(MechEcb ecb) ;

```

Uses MechEcb 24.

ecb A pointer to an event control block (ECB). The ECB must be the return value from mechEventNew, mechPolyEventNew or mechCreationEventNew.

36

The complication that arises when posting self directed events comes from finding where in the queue to insert the ECB. At first glance, it would seem that we need only put the event on the front of the event queue. However, should a state action generate two self directed events, simply placing them on the front of the event queue would result in the events being delivered in the reverse of the order that they were generated. It's an unusual case, but it is simple enough to cure by finding the first event on the event queue where the source instance and the target instance are different and performing the insertion of the ECB there.

```

36

\langle event \ generate \ 31a \rangle + \equiv

(150 153 156) ⊲35b 93b⊳

void

mechEventPostSelf(

MechEcb ecb)

{

assert(ecb->instOrClass.targetInst == ecb->srcInst) ;

/*

* Find the first event that is not self-directed.

*/

MechEcb iter ;

for (iter = eventQueueBegin(&eventQueue) ;

iter != eventQueueEnd(&eventQueue) ;

iter = iter->next) {

if (iter->srcInst != iter->instOrClass.targetInst) {

break ;

}

}

mechEventIncrRef(ecb) ;

eventQueueInsert(ecb, iter) ;

}

Uses eventQueue 28c and MechEcb 24.

```

Because the case where there are no event parameters is so common, we provide a set of convenience functions that can be used to allocate and queue an ECB for the various types of events and queues. In many cases this simplifies the coding significantly.

```

\langle inline \ functions \ 37a \rangle \equiv

37a

(149 152 155) 37b⊳

static inline

void

mechEventGenerate(

EventCode event,

MechInstance target,

MechInstance source)

{

mechEventPost(mechEventNew(event, target, source)) ;

}

Defines:

inline, used in chunk 101b.

Uses MechInstance 10.

\langle inline \ functions \ 37a \rangle + \equiv

37b

(149 152 155) ⊲37a 37c⊳

static inline

void

mechEventGenerateToSelf(

EventCode event,

MechInstance target)

{

mechEventPostSelf(mechEventNew(event, target, target)) ;

}

Defines:

inline, used in chunk 101b.

Uses MechInstance 10.

\langle inline \ functions \ 37a \rangle + \equiv

37c

(149 152 155) ⊲37b 38⊳

static inline

void

mechEventGeneratePolymorphic(

EventCode event,

MechInstance target,

MechInstance source)

{

mechEventPost(mechPolyEventNew(event, target, source)) ;

}

Defines:

inline, used in chunk 101b.

Uses MechInstance 10.

```

```

\langle inline \ functions \ 37a \rangle + \equiv

38

(149 152 155) ⊲37c 44 ⊳

static inline

void

mechEventGenerateCreation(

EventCode event,

MechClass targetClass,

MechInstance source)

{

mechEventPost(mechCreationEventNew(event, targetClass,

source));

}

Defines:

inline, used in chunk 101b.

Uses MechInstance 10.

```

# 4.3 Delayed Events

The concept of a delayed event is one where instead of the event begin posted to the event queue immediately, the mechanisms are requested to post the event at some time in the future. This implies that the mechanisms have access to some type of timing facility by which they can know that a given amount of time has elapsed and this implies that the mechanisms will hold on to the ECB until that future time has arrived.

There is one significant XUML rule associated with delayed events. There can be only one outstanding delayed event of a given event type between any sending / receiving pair of instances (which may be the same instance). This is another way of stating that delayed events are identified by their event name (or numerical encoding), the target instance and the source instance. There are a number of ways to interpret an attempt to generate what amounts to a duplicate delayed event. It could be considered an error, but that is inconvenient and goes against the grain of our attempts to minimize run-time errors. So the mechanisms regard an attempt to generate a delayed event of the same name between the same sending and receiving pair as a request to cancel the original event and create the new one at its newly given time. This turns out to be very convenient in practice, eliminating the need to perform checks. Cancelling and reinstating a new event turns out to be what is required in most circumstances.

To understand delayed events, it is necessary to understand the way the delayed event queue is maintained. The mechanisms have a delayed event queue where ECB's are placed awaiting to be posted. In servicing the delayed events, we are particularly trying to avoid doing any periodic computation. For example, we could treat the delayed event queue as a simple list and wake up periodically and run down the list decrementing time values and checking if any events have expired. Such a scheme is easy to implement, but in highly embedded and power sensitive application, periodic activity of this type is wasteful and deemed inappropriate.

In this implementation, we keep the delayed event queue in time relative order. Consider the following diagram.

Figure 2: Delayed Event Ordering

Here we show a conceptual timer that is counting down from 15 counts to zero. When the timer gets to zero, ECB #1 will have expired (because its delay value, relative to the timer, is 0) and is placed on the event queue. The timer is

then loaded with the delay value from ECB #2, namely 20. In this way, ECB #2 will have waited for the total time of all its predecessors plus its own delay time before being placed on the event queue.

Now consider state of the delayed event queue as originally shown in figure 2. If at this time a delayed event request, call it ECB # 4, arrives for 45, then the state of the queue after the request is inserted is shown in figure 3.

Figure 3: Delayed Event Ordering After Insertion

So ECB #4 will expire in 45 ticks because it will have waited for 15 ticks from ECB #1, 20 ticks from ECB #2 and 10 ticks for itself. Note also, that ECB #3 has had its delay time decreased by 10 ticks. This means that ECB #3 will expire at the same time as it would have had the insertion not taken place (*i.e.* 15 + 20 + 10 + 25 equals 15 + 20 + 35).

This design meets two important criteria; only a single source of timing is used and there is no periodic execution activity. The cost of meeting these criteria is the price paid to find the appropriate place in the delayed event queue when a delayed event is requested.

There are three functions supplied for dealing with delayed events:

• Post a delayed event.

40

- Cancel a delayed event.

- Query the remaining time for a delayed event.

While we are talking about time, the question of what time units must be answered. Time is specified in units of milliseconds.

```

⟨base types 11a⟩+≡ (149 152 155) ⊲23c 64a▷

typedef unsigned long int MechDelayTime;

Defines:

MechDelayTime, used in chunks 24, 41, 42, 44, 45a, 47, 48, 56, 58, 59, 105, 107-109, 125,

```

<sup>126, 138, 143, 144,</sup> and 150.

# 4.3.1 mechEventPostDelay

Posting a delayed event is just like posting a normal event, except that you must supply the number of milliseconds from now when the event is to be delivered.

- ecb A pointer to an event control block (ECB). The ECB must be the return value from mechEventNew(), mechPolyEventNew() or mechCreationEventNew().

- time The number of milliseconds in the future when the ECB pointed to by ecb is posted to the event queue. Note that this is the minimum number of milliseconds and more time may elapse before the event is actually posted.

```

\langle delayed \ event \ queue \ 42 \rangle \equiv

(150 153 156) 46⊳

void

mechEventPostDelay(

MechEcb ecb,

MechDelayTime time)

{

assert(ecb != NULL) ;

/*

* A delay time of 0 is valid, and the event will be

* queued immediately.

*/

if (time == 0) {

mechEventPost(ecb) ;

return ;

}

ecb->delay = mechMsecToTicks(time) ;

/*

* Stop the timing queue so we may examine it.

*/

stopDelayedQueueTiming() ;

/*

* If the event already exists, remove it.

*/

MechEcb prevEvent = findEvent(&delayedEventQueue,

ecb->srcInst, ecb->instOrClass.targetInst,

ecb->eventNumber) ;

if (prevEvent) {

removeFromDelayedQueue(prevEvent) ;

}

/*

* Insert the new event.

*/

insertIntoDelayedQueue(ecb) ;

assert(!eventQueueEmpty(&delayedEventQueue)) ;

/*

* Start the timer to expire for the first event

* on the queue.

*/

startDelayedQueueTiming() ;

}

```

Uses delayed EventQueue 28c, MechDelayTime 40, and MechEcb 24.

There are six main actions of this function.

- 1. First, a quick check is done to see if the delay time is zero. If is it, then the event is posted immediately. Delayed events are always posted as non-self directed events. Using a zero delay time is a "trick" that provides a means for a thread of control the *yield* up the processor by posting a delayed event directed at itself. This will place the event at the end of the event queue allowing all other pending events to be consumed before dispatching back to the yielding instance. The mechanism is crude, but sometimes necessary when one is forced to use the processor for unbounded computations (*e.g.* copying memory from one place to another).

- 2. Next, we convert the delay value from millisecond units to units of *ticks*. A tick is platform specific. Computers don't typically keep time at the lowest level in conventional human units. However, we would like to run the delayed event queue in system specific units to avoid as much unnecessary conversion as we can. This conversion will be described below for each supported platform.

- 3. Next, we stop the timing of the delayed event queue. More on this later but the goal of stopping the delayed event queue timing is to freeze the state of the queue so that we may operate on it.

- 4. Next we attempt to determine if there is already an event matching the one begin posted. This enforces the rule about not having two delayed events of the same type between the same sending / receiving pair. If one is found then it is removed.

- 5. Assured of no duplicates, the new event can be inserted into the timing queue. We will see how that happens below.

- 6. Finally, the timing of the delayed queue is started.

44

It is also convenient to define delayed event functions that generate events that have no supplemental event data.

```

(inline functions 37a) + \equiv

(149 152 155) ⊲38 45a⊳

static inline

void

mechEventGenerateDelayed(

EventCode event,

MechInstance target,

MechInstance source,

MechDelayTime delay)

{

mechEventPostDelay(mechEventNew(event, target, source),

delay);

}

Defines:

inline, used in chunk 101b.

Uses MechDelayTime 40 and MechInstance 10.

```

```

\langle inline \ functions \ 37a \rangle + \equiv

45a

(149\ 152\ 155) \lhd 44

static inline

void

mechEventGenerateDelayedToSelf(

EventCode event,

MechInstance target,

MechDelayTime delay)

{

mechEventPostDelay(mechEventNew(event, target, target),

delay);

}

Defines:

inline, used in chunk 101b.

Uses MechDelayTime 40 and MechInstance 10.

```

#### 4.3.2 mechEventDelayCancel

Cancelling a delayed event is one of the more complicated delayed event operations. We must account for the various places where a delayed event may be queued.

A delayed event may be in one of two places:

- 1. In the delayed event queue awaiting either waiting for its time to expire or having already been marked as expired.

- 2. In the event queue awaiting dispatch.

We will have more to say about event dispatch below, but it is possible to try to cancel an event after its time has expired but before it has been delivered to the target instance. The mechanisms make the guarantee that after invoking mechEventDelayCancel the application can be assured that the event will *not* be delivered until such time as it is posted again. Note that it is possible to attempt to cancel a delayed event after it has already been delivered. This is not an error. Unfortunately, the mechanisms cannot turn time backwards.

45b

$(149 \ 152 \ 155) \lhd 41 \ 47 \triangleright$

⟨external scoped functions 15⟩+≡

extern void

mechEventDelayCancel(

EventCode event,

MechInstance targetInst,

MechInstance srcInst);

Uses MechInstance 10.

event The number of the event.

targetInst A pointer to the instance structure that is to receive the event.

**srcInst** A pointer to the instance structure that is sending the event. Events generated outside of a class instance may set this argument to NULL.

```

\langle delayed \ event \ queue \ 42 \rangle + \equiv

46

(150 153 156) ⊲42 48⊳

void

mechEventDelayCancel(

EventCode event,

MechInstance targetInst,

MechInstance srcInst)

{

assert(targetInst != NULL) ;

/*

* Stop delayed queue so that we may examine it.

*/

stopDelayedQueueTiming() ;

/*

* Search for the event in the delayed event queue.

*/

MechEcb foundEvent = findEvent(&delayedEventQueue,

srcInst, targetInst, event) ;

if (foundEvent) {

/*

* Removing from the delayed queue requires

* additional processing of the delay times.

*/

removeFromDelayedQueue(foundEvent) ;

} else {

/*

* If the event is not in the delayed queue, then

* search the event queue. The timer could have

* expired and the event placed in the queue.

*/

foundEvent = findEvent(&eventQueue, srcInst,

targetInst, event) ;

if (foundEvent) {